JTAG (Joint Test Action Group) je dobře zavedený standard IEEE 1149.1, který byl vyvinut v roce 1980 k vyřešení výrobních problémů, které se vyskytly v elektronických deskách resp. desky plošných spojů . Tato technologie se používá k zajištění dostatečného testovacího přístupu pro každou komplexní desku, když testovací přístup klesal. Byla tak spuštěna technologie boundary scan & standard JTAG resp Specifikace JTAG Je založena. Složitost elektroniky se každým dnem zvyšuje, takže specifikace JTAG se stala uznávaným testovacím formátem pro testování komplikovaných a kompaktních elektronických jednotek. Tento článek pojednává o přehledu a JTAG protokol – práce s aplikacemi.

Co je JTAG?

Název, který je dán standardnímu testovacímu přístupovému portu IEEE 1149.1 a architektuře Boundary-Scan Architecture, je známý jako JTAG (Joint Test Action Group). Tato architektura boundary scan se většinou používá v počítači procesory protože první procesor s JTAG vydal Intel. Tento standard IEEE jednoduše definuje, jak jsou obvody počítače testovány, aby se potvrdilo, že po výrobním procesu fungují správně. Na deskách plošných spojů se provádějí testy pro kontrolu pájených spojů.

Joint Test Action Group poskytuje testerům pohled na piny s každou IC podložkou, což pomáhá při identifikaci jakýchkoli závad na desce plošných spojů. Jakmile je tento protokol propojen s čipem, může k čipu připojit sondu tím, že vývojáři umožní ovládat čip i jeho spojení s jinými čipy. Rozhraní se skupinou Joint Test Action mohou také vývojáři použít pro kopírování firmwaru do energeticky nezávislé paměti v elektronickém zařízení.

Konfigurace/Pin Out

Společná testovací akční skupina obsahuje 20 kolíků, kde každý kolík a jeho funkce jsou popsány níže.

Pin1 (VTref): Toto je pin cílového referenčního napětí, který se používá k připojení k hlavnímu napájecímu zdroji cíle, který se pohybuje od 1,5 do 5,0 V DC.

Pin2 (Vsupply): Toto je cílové napájecí napětí, které se používá pro připojení hlavního napájecího zdroje cílového napětí 1,5VDC – 5,0VDC.

Pin3 (nTRST): Toto je testovací resetovací kolík, který se používá k resetování stavového stroje řadiče TAP.

Piny (4, 6, 8, 10, 12, 14, 16, 18 a 20): Jedná se o běžné piny GND.

Pin5 (TDI): Toto jsou testovací data v kolíku. Tato data se přenesou do cílového zařízení. Tento kolík musí být vytažen nahoru za definovaných podmínek na cílové desce.

Pin7 (TMS): Toto je kolík stavu testovacího režimu, který je vytažen, aby se určil další stav stavového stroje řadiče TAP.

Pin9 (TCK): Toto je testovací hodinový kolík, který synchronizuje operace vnitřního stavového stroje v řadiči TAP.

Pin11 (RTCK): Toto je TCK pin Input Return, který se používá v zařízeních podporujících adaptivní taktování.

Pin13 (TDO): Toto je kolík Test Data Out, takže data jsou přesunuta z cílového zařízení do Flyswatteru.

Pin15 (nSRST): Toto je pin pro resetování cílového systému, který je připojen k hlavnímu resetovacímu signálu cíle.

Kolíky 17 a 19 (NC): Nejsou to spojené kolíky.

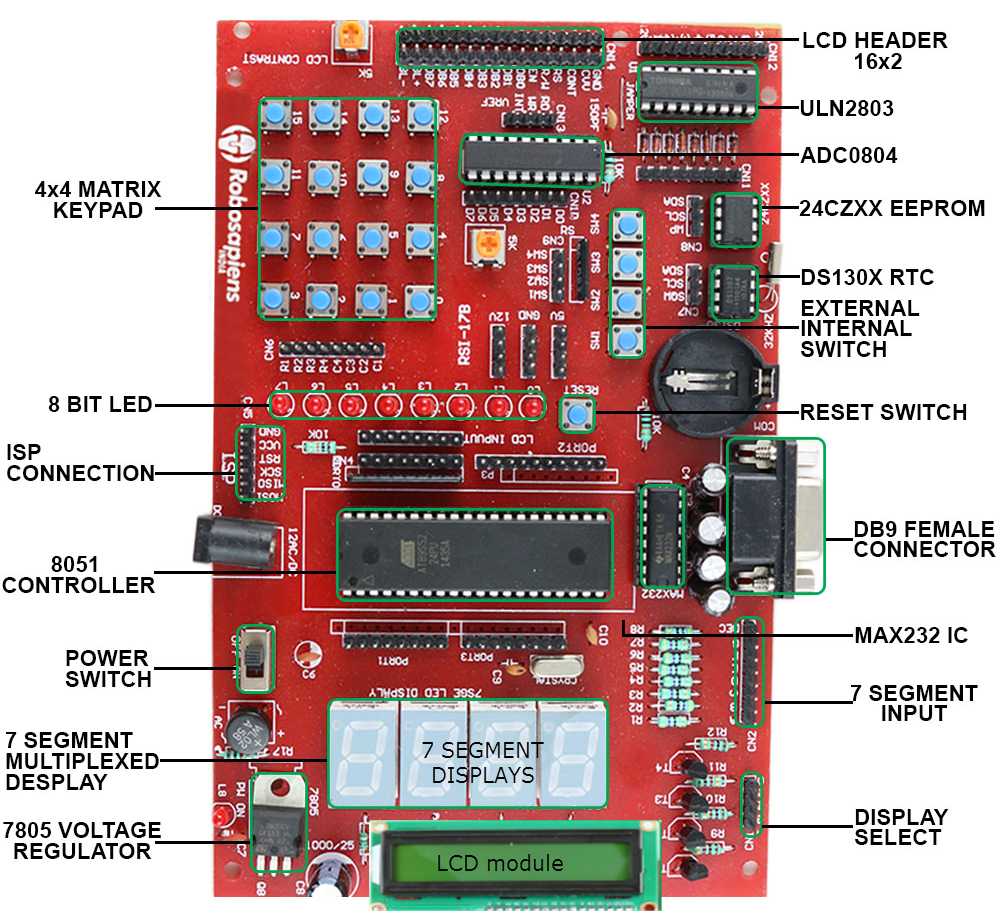

JTAG funguje

Původní použití JTAG je pro testování hranic. Zde je jednoduchá deska s plošnými spoji obsahující dva integrované obvody, jako je CPU a FPGA . Typická deska může obsahovat mnoho integrovaných obvodů. Obecně platí, že integrované obvody obsahují mnoho kolíků, které jsou spojeny společně s mnoha připojeními. Zde jsou na následujícím schématu znázorněny pouze čtyři zapojení.

Pokud tedy navrhujete mnoho desek, kde každá deska má tisíce připojení. V tom jsou některé špatné desky. Musíme tedy zkontrolovat, která deska funguje a která nefunguje. K tomu byla navržena Společná testovací akční skupina.

Tento protokol může používat řídicí kolíky všech čipů, ale v následujícím schématu Společná testovací akční skupina vytvoří všechny výstupní kolíky CPU a všechny vstupní kolíky FPGA. Poté, přenosem určitého množství dat z pinů CPU a čtením hodnot pinů z FPGA, JTAG uvádí, že připojení desky PCB jsou v pořádku.

Společná testovací akční skupina ve skutečnosti zahrnuje čtyři logické signály TDI, TDO, TMS a TCK. A tyto signály je třeba propojit zvláštním způsobem. Nejprve jsou TMS a TCK zapojeny paralelně ke všem integrovaným obvodům JTAG.

Poté jsou oba TDI a TDO spojeny pro vytvoření řetězu. Jak můžete pozorovat, každý IC kompatibilní s JTAG obsahuje 4 piny, které se používají pro JTAG, kde 3 piny jsou vstupy a 4. pin je výstup. Pátý kolík jako TRST je volitelný. Piny JTAG obvykle nejsou sdíleny pro jiné účely.

Použitím Joint Test Action Group využívají všechny IC hraniční testování, jehož původní důvod je vytvořen JTAG. V současné době bylo použití tohoto protokolu rozšířeno tak, aby umožňovalo různé věci, jako je konfigurace FPGA a poté se JTAG používá v jádře FPGA pro účely ladění.

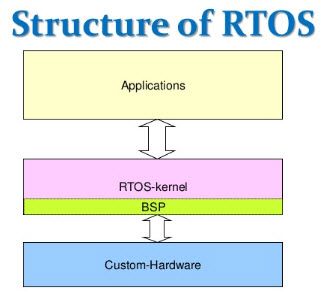

Architektura JTAG

Architektura JTAG je uvedena níže. V této architektuře jsou všechny signály mezi základní logikou zařízení a kolíky přerušeny prostřednictvím sériové skenovací cesty nazývané BSR nebo Boundary Scan Register. Tento BSR zahrnuje různé „buňky“ boundary scan. Obecně tyto buňky hraničního skenování nejsou viditelné, ale lze je použít k nastavení nebo čtení hodnot v testovacím režimu z kolíků zařízení.

Rozhraní JTAG nazývané TAP nebo Test Access Port používá různé signály pro podporu operace boundary scan, jako jsou TCK, TMS, TDI, TDO a TRST.

- Signál TCK nebo Test Clock jednoduše synchronizuje vnitřní operace stavového automatu.

- Signál TMS nebo Test Mode Select je vzorkován na rostoucí hraně testovacího hodinového signálu pro rozhodnutí o dalším stavu.

- Signál TDI nebo Test Data In značí posunutá data do testovacího zařízení jinak programovací logiky. Jakmile je vnitřní stavový automat ve správném stavu, je vzorkován na rostoucí hraně TCK.

- Signál TDO nebo Test Data Out označuje posunutá data testovacího zařízení, jinak programovací logiku. Jakmile je vnitřní stavový automat ve správném stavu, pak je platný na sestupné hraně TCK

- TRST nebo Test Reset je volitelný pin, který se používá k resetování stavového stroje ovladače TAP.

Ovladač TAP

Testovací přístupový bod v architektuře JTAG se skládá z řadiče TAP, registru instrukcí a registrů testovacích dat. Tento regulátor obsahuje testovací stavový stroj, který je zodpovědný za čtení signálů TMS a TCK. Zde se datový i/p pin jednoduše používá k načítání dat do hraničních buněk mezi jádrem IC a fyzickými piny a také k načítání dat do jednoho z datových registrů nebo do registru instrukcí. Data o/p pin se používá pro čtení dat buď z registrů nebo hraničních buněk.

Stavový automat regulátoru TAP je řízen TMS a je taktován TCK. Stavový stroj používá dvě cesty pro označení dvou různých režimů, jako je instrukční režim a datový režim.

Registry

V rámci boundary scan jsou k dispozici dva druhy registrů. Každé vyhovující zařízení obsahuje minimálně dva nebo více datových registrů a jeden instrukční registr.

Registr instrukcí

Registr instrukcí se používá k uložení aktuální instrukce. Takže jeho data používá řadič TAP k rozhodnutí, co provést se získanými signály. Data instrukčního registru budou nejčastěji popisovat, do kterého z datových registrů musí být předány signály.

Datové registry

Datové registry jsou dostupné ve třech typech: BSR (Boundary Scan Register), BYPASS a registr ID CODES. Mohou zde být i další datové registry, které však nejsou nutné jako prvek standardu JTAG.

Boundary Scan Register (BSR)

BSR je hlavní registr testovacích dat, který se používá k přesunu dat z a na I/O piny zařízení.

BYPASS

Bypass je jednobitový registr sloužící k předávání dat z TDI – TDO. Umožňuje tedy testovat další zařízení v okruhu s minimální režií.

ID KÓDY

Tento typ datového registru obsahuje ID kód a také číslo revize zařízení. Tato data tedy umožňují připojení zařízení k jeho souboru BSDL (Boundary Scan Description Language). Tento soubor obsahoval podrobnosti konfigurace Boundary Scan pro zařízení.

Fungování JTAG je zpočátku zvoleno instrukčním režimem, kde jeden ze stavů v tomto režimu „cesta“ umožňuje operátorovi hodiny v rámci instrukce TDI. Poté se stavový stroj vyvíjí, dokud se nepřeuspořádá. Dalším krokem pro většinu pokynů je výběr datového režimu. Takže v tomto režimu jsou data načtena přes TDI, aby se četla z TDO. Pro TDI & TDO budou datové cesty uspořádány v souladu s instrukcí, která byla taktovana. Po dokončení operace čtení/zápisu se stavový stroj opět rozvine do stavu reset.

Rozdíl mezi JTAG a UART

Rozdíl mezi JTAG a UART zahrnuje následující.

| JTAG |

UART |

| Termín „JTAG“ znamená Joint Test Action Group. | Termín ' UART ” znamená Universal Asynchronous Receiver/Transmitter. |

| Jedná se o synchronní rozhraní, které využívá vestavěný hardware pro programování blesku . | UART je asynchronní rozhraní, které využívá bootloader, který běží v paměti. |

| Je to sada testovacích portů, které slouží k ladění, ale lze je také použít k programování firmwaru (což se běžně dělá).

|

UART je typ čipu, který řídí komunikaci do a ze zařízení, jako je mikrokontrolér, ROM, RAM atd. Většinou jde o sériové připojení, které nám umožňuje komunikovat se zařízením. |

| Ty jsou k dispozici ve čtyřech typech TDI, TDO, TCK, TMS & TRST. | Ty jsou k dispozici ve dvou typech němý UART a FIFO UART. |

| Joint Test Action Group je sériové programování nebo protokol pro přístup k datům, který se používá při propojování mikrokontrolérů a souvisejících zařízení. | UART je jeden druh čipu, jinak podsoučást mikrokontroléru, který se používá k poskytování hardwaru pro generování asynchronního sériového toku, jako je RS-232/RS-485. |

| Komponenty JTAG jsou procesory, FPGA, CPLD , atd. | Komponenty UART jsou generátor CLK, I/O posuvné registry, vysílací nebo přijímací vyrovnávací paměti, vyrovnávací paměť systémové datové sběrnice, řídicí logika čtení nebo zápisu atd. |

JTAG protokolový analyzátor

JTAG Protocol Analyzer jako PGY-JTAG-EX-PD je jeden druh Protocol Analyzer obsahující některé funkce pro zachycení a ladění komunikace mezi hostitelem a testovaným designem. Tento typ analyzátoru je předním nástrojem, který umožňuje testovacím a návrhářským inženýrům testovat konkrétní návrhy JTAG pro jejich specifikace prostřednictvím uspořádání PGY-JTAG-EX-PD jako Master nebo Slave pro generování provozu JTAG a dekódování dekódovacích paketů Protokol Joint Test Action Group.

Funkce

Mezi vlastnosti analyzátoru protokolu JTAG patří následující.

- Podporuje až 25MHz frekvencí JTAG.

- Generuje provoz JTAG a dekódování protokolu pro sběrnici současně.

- Má JTAG Master Capability.

- Variabilní datové rychlosti JTAG a pracovní cyklus.

- Uživatelsky definované zpoždění TDI a TCK.

- Rozhraní USB 2.0 nebo 3.0 hostitelského počítače.

- Analýza chyb v rámci dekódování protokolu

- Časový diagram sběrnice dekódovaný protokolem.

- Nepřetržitý přenos dat protokolu do hostitelského počítače pro zajištění velké vyrovnávací paměti.

- Seznam aktivit protokolu.

- Různými rychlostmi lze napsat cvičný skript pro kombinování generování více datových rámců.

Časový diagram

The časový diagram JTAG protokol je uveden níže. V následujícím diagramu zůstává kolík TDO ve stavu vysoké impedance s výjimkou stavu ovladače shift-IR/shift-DR.

V podmínkách řadiče shift-IR a Shift-DR je TDO pin aktualizován na sestupné hraně TCK přes Target a vzorkován na rostoucí hraně TCK přes Host.

Oba piny TDI a TMS jsou jednoduše vzorkovány na rostoucí hraně TCK přes Target. Aktualizováno na sestupném okraji, jinak TCK prostřednictvím hostitele.

Aplikace

The JTAG aplikace zahrnout následující.

- Skupina Joint Test Action Group se v procesorech často používá k poskytování práva na vstup do jejich emulačních nebo ladicích funkcí.

- Všechny CPLD a FPGA toto používají jako rozhraní pro přístup k jejich programovacím funkcím.

- Používá se pro testování DPS bez fyzického přístupu

- Používá se pro výrobní testy na úrovni desek.

Tak, to je všechno o přehled JTAG – konfigurace pinů, práce s aplikacemi. Průmyslový standard JTAG se používá pro ověření návrhu i testování DPS po výrobě. Zde je otázka pro vás, JTAG znamená?