The fázově uzavřená smyčka je jedním ze základních bloků v moderních elektronických systémech. Obvykle se používá v multimédiích, komunikaci a v mnoha dalších aplikacích. Existují dva různé typy PLL - lineární a nelineární. Nelineární je obtížné a složité navrhnout v reálném světě, ale teorie lineárního řízení je dobře modelována v analogových PLL. PLL prokázal, že lineární model je dostatečný pro většinu elektronických aplikací.

Co je to fázově blokovaná smyčka?

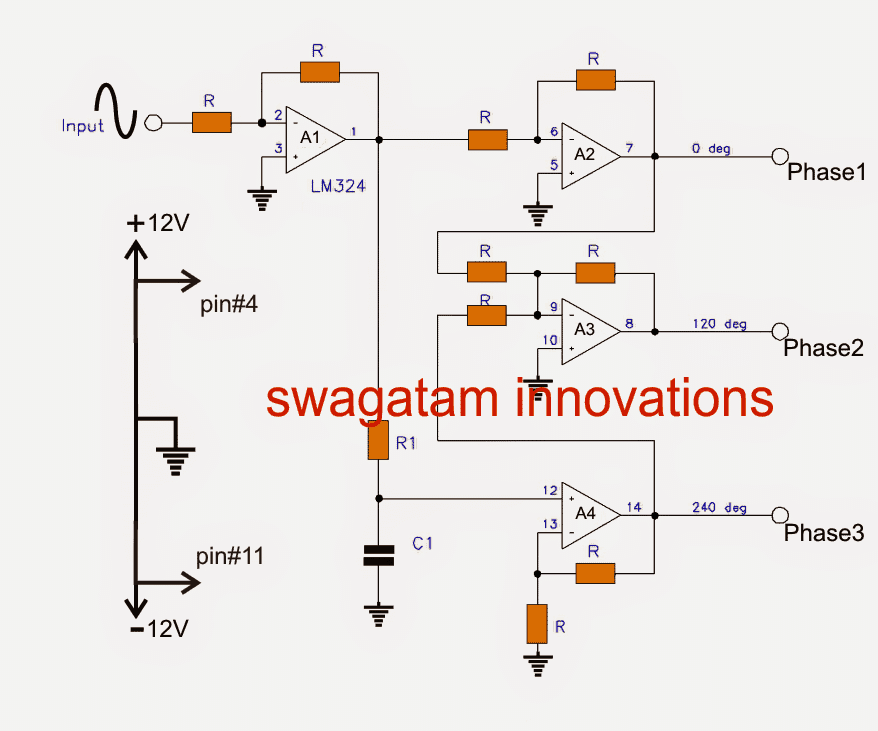

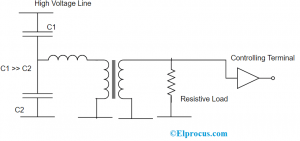

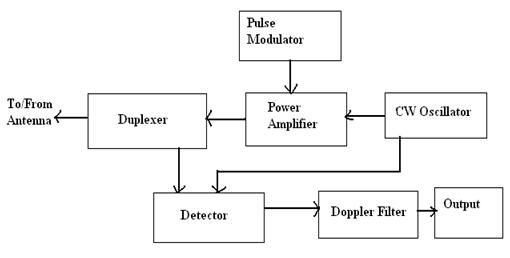

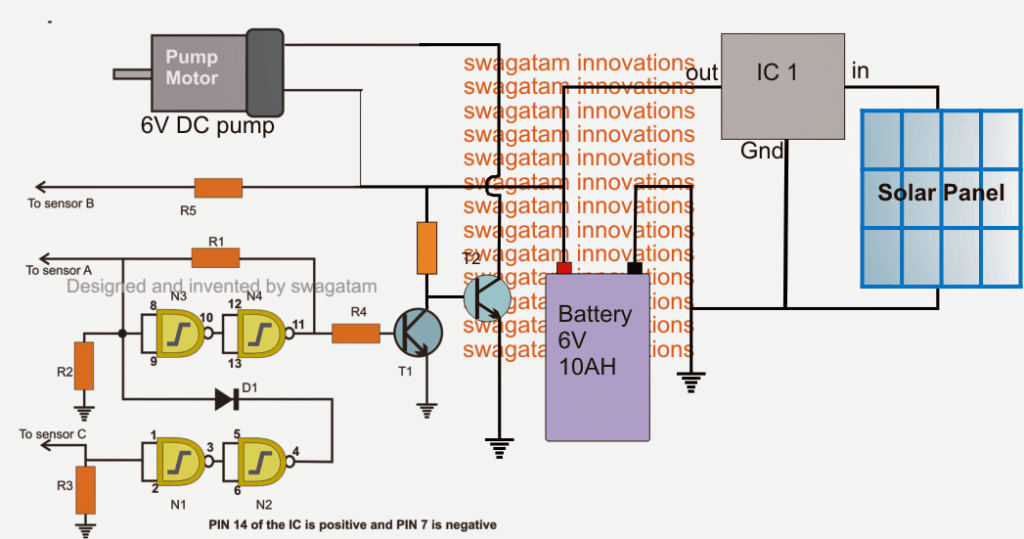

Fázová smyčka se skládá z fázového detektoru a napěťově řízeného oscilátoru. Výstupem fázového detektoru je vstup napěťově řízeného oscilátoru (VCO) a výstup VCO je připojen k jednomu ze vstupů fázového detektoru, který je zobrazen níže v základním blokovém schématu. Když jsou tato dvě zařízení navzájem napájena, tvoří se smyčka.

ZÁKLADNÍ SCHÉMA FÁZOVÉ ZABLOKOVANÉ SMYČKY

Blokové schéma a pracovní princip PLL

Fázově uzavřená smyčka se skládá z fázového detektoru, a napěťově řízený oscilátor a mezi nimi je upevněn dolní propust. Vstupní signál „Vi“ se vstupní frekvencí „Fi“ je povolen fázovým detektorem. V zásadě je to fázový detektor komparátor který porovnává vstupní frekvenci fi prostřednictvím zpětnovazební frekvence fo. Výstup fázového detektoru je (fi + fo), což je stejnosměrné napětí. Z fázového detektoru, tj. Stejnosměrného napětí, se vstupuje do nízkofrekvenčního filtru (LPF), odstraňuje vysokofrekvenční šum a vytváří stabilní stejnosměrnou hladinu, tj. Fi-Fo. Vf je také dynamickou charakteristikou PLL.

Blokové schéma PLL

Výstup dolnofrekvenčního filtru, tj. Úroveň stejnosměrného proudu, se předává VCO. Vstupní signál je přímo úměrný výstupní frekvenci VCO (fo). Vstupní a výstupní frekvence se porovnávají a upravují zpětnovazební smyčkou, dokud se výstupní frekvence nebude rovnat vstupní frekvenci. Proto PLL funguje jako volný běh, zachycení a fázový zámek.

Pokud není připojeno žádné vstupní napětí, říká se, že jde o volně běžící fázi. Jakmile se vstupní frekvence aplikovaná na VOC změní a vytvoří výstupní frekvenci pro srovnání, nazývá se to fáze snímání. Níže uvedený obrázek ukazuje blokové schéma PLL.

Detektor smyčky fázového závěsu

Detektor fázově uzavřené smyčky porovnává vstupní frekvenci a výstupní frekvenci VCO a vytváří stejnosměrné napětí, které je přímo úměrné fázovému rozlišení obou frekvencí. Analogové a digitální signály se používají ve smyčce fázového závěsu. Většina monolitického PLL integrované obvody použijte analogový fázový detektor a většina fázových detektorů je z digitálního typu. V analogových fázových detektorech se běžně používá dvojitě vyvážený směšovací obvod. Níže jsou uvedeny některé běžné fázové detektory:

Exkluzivní detektor fází NEBO

Exkluzivní fázový detektor OR je typu CMOS IC 4070. Vstupní a výstupní frekvence jsou aplikovány na fázový detektor EX OR. Chcete-li získat vysoký výstup, měl by být alespoň jeden vstup nízký a ostatní podmínky výstupu jsou nízké, což je uvedeno v následující tabulce pravdivosti. Uvažujme tvar vlny, vstupní a výstupní frekvence, tj. Fi a fo mají fázový rozdíl 0 stupňů. Pak bude stejnosměrné výstupní napětí komparátoru funkcí fázového rozdílu mezi dvěma vstupy.

| být | fo | Vdc |

nízký | nízký | nízký |

nízký | vysoký | vysoký |

vysoký | Nízký | vysoký |

Vysoký | Vysoký | nízký |

Funkce fázového rozdílu mezi fi a fo jsou znázorněny v grafu stejnosměrného výstupního napětí. Pokud je fázový detektor 180 stupňů, pak je výstupní napětí maximální. Pokud jsou vstupní i výstupní frekvence obdélníkové, použije se tento typ fázových detektorů.

Exkluzivní detektor fází NEBO

Fázový detektor spouštění hran

Detektor hranové spouštěcí fáze se používá, když jsou vstupní a výstupní frekvence v pulzním průběhu, který je menší než 50% pracovní cyklus. Klopný obvod R-S se používá pro fázové detektory, což je znázorněno na následujícím obrázku. Do z R-S žabky , dvě brány NOR jsou vzájemně spojeny. Výstup fázového detektoru může změnit svůj logický stav spuštěním klopného obvodu R-S. Kladná hrana vstupních a výstupních frekvencí může změnit výstup fázového detektoru.

Fázový detektor spouštění hran

Monolitický fázový detektor

Monolitický fázový detektor je typu CMOS, tj. IC 4044. Je vysoce kompenzován harmonickou citlivostí a problémy pracovního cyklu jsou opuštěny, protože obvod může reagovat pouze na přechod vstupního signálu. V kritických aplikacích je to nejvíce horečný fázový detektor. Nezávislé variace amplitudy jsou prosté fázové chyby, výstupního chybového napětí a pracovního cyklu vstupních průběhů.

Aplikace fázově uzavřené smyčky

- Demodulační sítě FM pro provoz FM

- Používá se v ovládání otáček motoru a sledovací filtry.

- Používá se při dekódování s frekvenčním posunem pro demodulační nosné frekvence.

- Používá se v čase na digitální převaděče.

- Používá se pro redukci chvění, potlačení zkosení, zotavení hodin.

Jedná se o pracovní a provozní princip fázově uzavřené smyčky a její aplikace. Doufáme, že informace uvedené v článku vám pomohou vědět něco o projektu a porozumět mu. Dále, pokud máte jakékoli dotazy týkající se tohoto článku a dále elektrické a elektronické projekty můžete komentovat v níže uvedené části. Zde je otázka, jaký je nejlepší způsob simulace PLL pro stabilitu?

Fotografické kredity:

- Blokové schéma PLL obvod dnes

- Exkluzivní detektor fází NEBO sanfoundry

- Fázový detektor spouštění hran LEARNABOUT-ELECTRONICS