Pro provádění počítačového programu vyžaduje synchronní práci více než jedné součásti počítače. Například, Procesory - poskytování nezbytných řídicích informací, adres… atd., Sběrnic - pro přenos informací a dat do az paměti do I / O zařízení… atd. Zajímavým faktorem systému by byl způsob, jakým zpracovává přenos informací mezi procesorem, pamětí a I / O zařízeními. Procesory obvykle řídí celý proces přenosu dat, a to hned od zahájení přenosu do úložiště dat v cílovém místě. To zvyšuje zátěž procesoru a většinu času zůstává v ideálním stavu, čímž se snižuje účinnost systému. Pro urychlení přenosu dat mezi I / O zařízeními a pamětí funguje DMA řadič jako hlavní stanice. Řadič DMA přenáší data s minimálním zásahem procesoru.

Co je řadič DMA?

Termín DMA znamená přímý přístup do paměti. Hardwarové zařízení používané pro přímý přístup do paměti se nazývá řadič DMA. DMA controller je řídicí jednotka , součást I / O zařízení obvod rozhraní , který může přenášet bloky dat mezi I / O zařízeními a hlavní pamětí s minimálním zásahem procesoru.

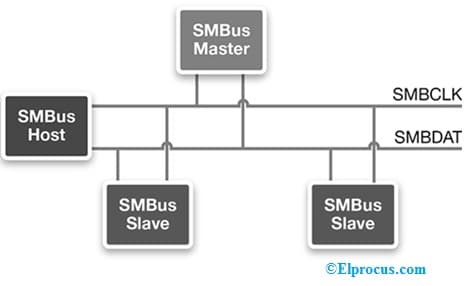

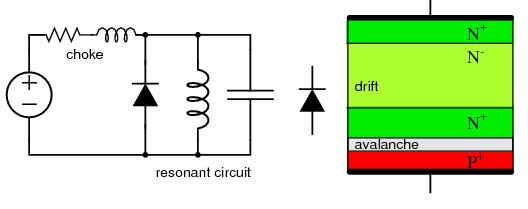

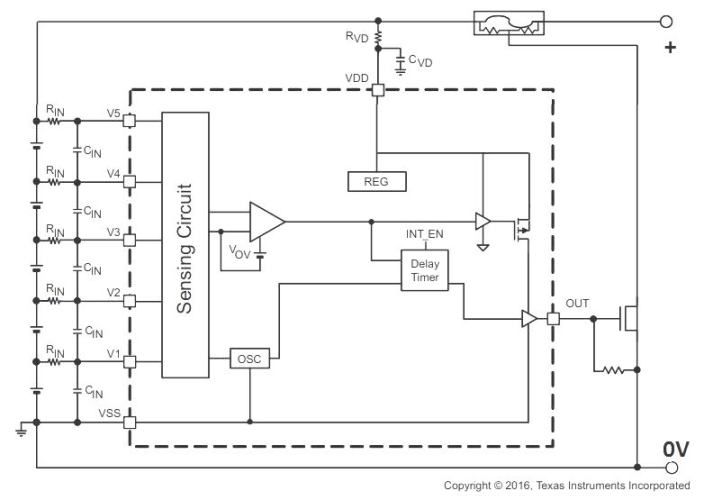

Schéma řadiče DMA v počítačové architektuře

Řadič DMA poskytuje rozhraní mezi sběrnicí a vstupně-výstupními zařízeními. Přestože přenáší data bez zásahu procesoru, je řízen procesorem. Procesor inicializuje řadič DMA zasláním počáteční adresy, počtu slov v datovém bloku a směru přenosu dat, tj. z I / O zařízení do paměti nebo z hlavní paměti do I / O zařízení. K řadiči DMA lze připojit více než jedno externí zařízení.

DMA v počítačové architektuře

Řadič DMA obsahuje jednotku adresy pro generování adres a výběr I / O zařízení pro přenos. Obsahuje také řídicí jednotku a počet dat pro udržování počtů počtu přenesených bloků a udávající směr přenosu dat. Když je přenos dokončen, DMA informuje procesor zvýšením přerušení. Typické blokové schéma řadiče DMA je znázorněno na obrázku níže.

Typické blokové schéma řadiče DMA

Práce řadiče DMA

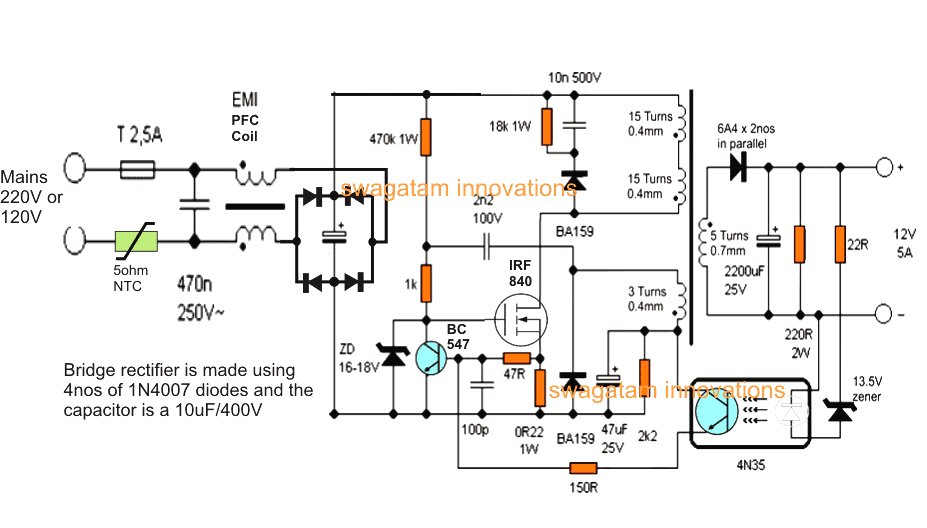

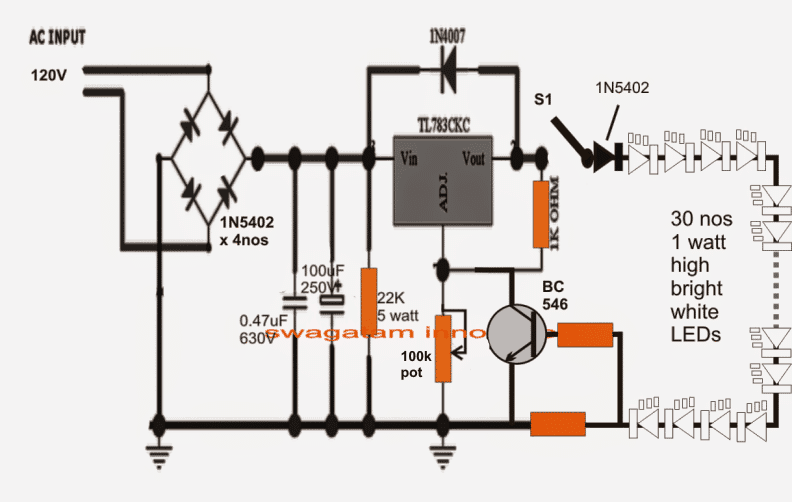

Řadič DMA musí pro přenos dat sdílet sběrnici s procesorem. Zařízení, které v danou dobu drží sběrnici, se nazývá master sběrnice. Když je třeba provést přenos ze vstupně-výstupního zařízení do paměti nebo naopak, procesor zastaví provádění aktuálního programu, v krocích Program čítač, přesune data po zásobníku a poté pošle signál DMA select do řadiče DMA přes adresovou sběrnici.

Pokud je řadič DMA volný, požaduje řízení sběrnice od procesoru zvýšením signálu požadavku na sběrnici. Procesor uděluje sběrnici řadiči zvýšením signálu přidělení sběrnice, nyní je řadičem DMA řadič DMA. Procesor inicializuje řadič DMA odesláním adres paměti, počtu bloků dat, která mají být přenesena, a směru přenosu dat. Po přiřazení úlohy přenosu dat řadiči DMA místo ideálního čekání na dokončení přenosu dat procesor obnoví provádění programu po načtení pokynů ze zásobníku.

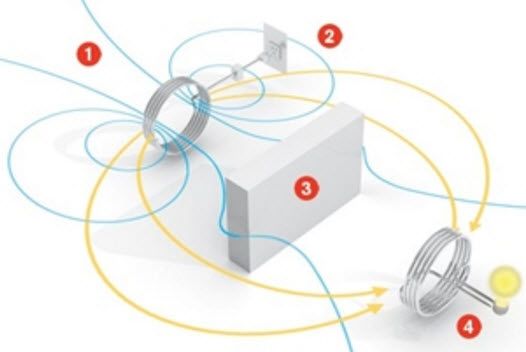

Přenos dat v počítači řadičem DMA

Řadič DMA má nyní plnou kontrolu nad sběrnicemi a může komunikovat přímo s pamětí a I / O zařízeními nezávisle na CPU. Provádí přenos dat podle řídicích pokynů přijatých procesorem. Po dokončení přenosu dat deaktivuje signál požadavku na sběrnici a CPU deaktivuje signál pro přidělení sběrnice, čímž přesune řízení sběrnic na CPU.

Když I / O zařízení chce zahájit přenos, odešle signál požadavku DMA na řadič DMA, který řadič potvrdí, pokud je volný. Poté ovladač požaduje procesor pro sběrnici a zvyšuje signál požadavku na sběrnici. Po přijetí signálu sběrnicového povolení přenáší data ze zařízení. U n směrovaného řadiče DMA lze připojit n počet externích zařízení.

DMA přenáší data ve třech režimech, které zahrnují následující.

na) Burst režim : V tomto režimu DMA předává sběrnice do CPU až po dokončení celého přenosu dat. Mezitím, pokud CPU vyžaduje sběrnici, musí zůstat ideální a čekat na přenos dat.

b) Režim krádeže cyklu : V tomto režimu poskytuje DMA řízení sběrnic do CPU po přenosu každého bajtu. Neustále vydává požadavek na řízení sběrnice, provádí přenos jednoho bajtu a vrací sběrnici. Díky tomu CPU nemusí dlouho čekat, pokud potřebuje sběrnici pro úkol s vyšší prioritou.

C) Transparentní režim: Zde DMA přenáší data pouze tehdy, když CPU provádí instrukci, která nevyžaduje použití sběrnic.

Řadič 8237 DMA

- 8237 má 4 I / O kanály spolu s flexibilitou zvyšování počtu kanálů.

- Každý kanál lze naprogramovat samostatně a má 64k adresu a schopnost dat.

- Řídicí blok časování, řídicí blok programových příkazů, blok prioritního kodéru jsou tři hlavní bloky 8237A.

- Interní časování a externí řídicí signály jsou řízeny řídicím blokem časování.

- Různé příkazy dané mikroprocesorem do DMA jsou dekódovány řídicím blokem programových příkazů.

- Kterému kanálu musí být přidělena nejvyšší priorita, určuje priorita blok kodéru .

8237A má 27 interních registrů.

8237A pracuje ve dvou cyklech - Ideální cyklus a aktivní cyklus, kde každý cyklus obsahuje 7 samostatných stavů složených z jedné hodinové periody.

S0- První stav, kdy řadič požádal o sběrnici a čeká na potvrzení od procesoru.

S1, S2, S3, S4 se nazývají pracovní stavy 8237A, kde dochází ke skutečnému přenosu dat. Pokud je na přenos zapotřebí více času, přidají se stavy SW mezi tyto stavy.

U přenosu z paměti do paměti je třeba provést přenosy čtení z paměti a zápis do paměti. Pro jeden přenos je vyžadováno osm států. První čtyři stavy s indexy S11, S12, S13, S14 provádějí přenos čtení z paměti a další čtyři S21, S22, S23, S24 jsou určeny pro přenos do paměti.

DMA přejde do ideálního stavu, když žádný kanál nepožaduje službu a neprovede stav SI. SI je neaktivní stav, kdy je DMA neaktivní, dokud neobdrží požadavek. V tomto stavu je DMA ve stavu programu, kdy procesor může programovat DMA.

Když je DMA v ideálním stavu a neobdrží žádné další požadavky na kanál, odešle signál HRQ do procesoru a vstoupí do aktivního stavu, kde může zahájit přenos dat buď v režimu série, režimu krádeže cyklu nebo transparentního režimu.

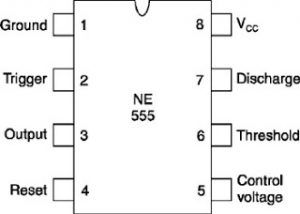

8237 Pinový diagram

Řadič 8257 DMA

Po spárování s jedním zařízením I / O portem Intel 8212 tvoří řadič 8257 DMA kompletní 4kanálový Řadič DMA . Po obdržení žádosti o převod řídicí jednotka 8257

- Získá kontrolu nad systémovou sběrnicí od procesoru.

- Periferní zařízení připojené k kanálu s nejvyšší prioritou je potvrzeno.

- Nejméně významné bity adresy paměti se přesouvají po adresních řádcích A0-A7 systémové sběrnice.

- Nejvýznamnější 8 bitů adresy paměti jsou přenášeny na 8212 I / O port přes datové linky.

- Generuje příslušné řídicí signály pro přenos dat mezi periferiemi a adresovanými paměťovými místy.

- Když se přenese zadaný počet bajtů, řadič informuje procesor o ukončení přenosu aktivací výstupu počtu terminálů (TC).

Pro každý kanál obsahuje 8257 dva 16bitové registry - 1) Registr adres DMA a 2) Registr počtu terminálů, který by měl být inicializován před povolením kanálu. Adresa prvního paměťového místa, ke kterému se má přistupovat, se načte do registru adres DMA. Nižší řád 14 bitů hodnoty načtené do registru počtu terminálů označuje počet cyklů DMA minus jeden před aktivací výstupu počtu terminálů. Typ operace pro kanál je indikován nejvýznamnějšími dvěma bity registru počtu terminálů.

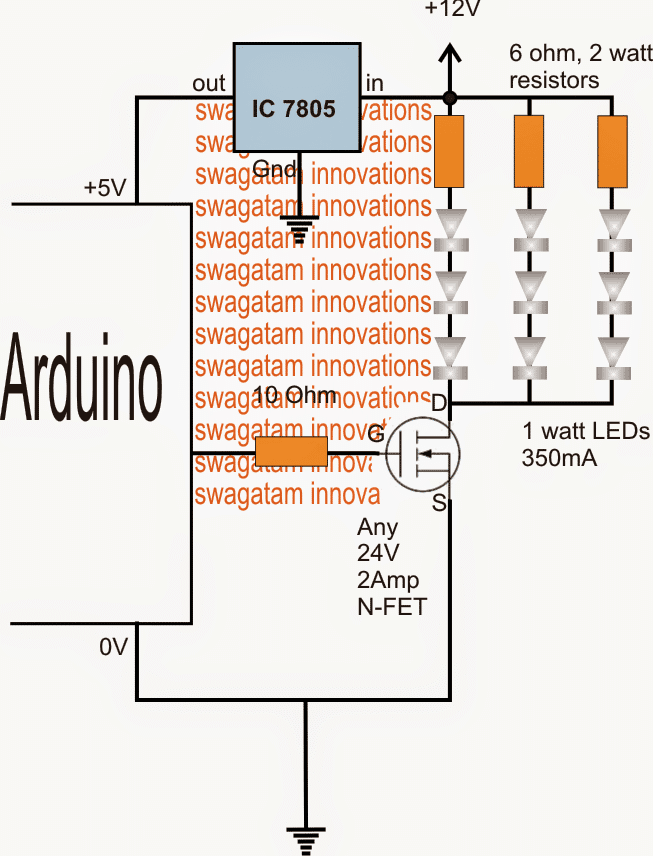

8257 Pinový diagram

Výhody a nevýhody řadiče DMA

Mezi výhody a nevýhody řadiče DMA patří následující.

Výhody

- DMA zrychluje operace paměti tím, že obchází zapojení CPU.

- Pracovní přetížení na CPU se snižuje.

- Pro každý přenos je vyžadováno pouze několik počtů hodinových cyklů

Nevýhody

- Problém s koherencí mezipaměti lze vidět, když se pro přenos dat používá DMA.

- Zvyšuje cenu systému.

DMA ( Přímý přístup do paměti ) řadič se používá v grafických kartách, síťových kartách, zvukových kartách atd ... DMA se také používá pro přenos uvnitř čipu ve vícejádrových procesorech. Při provozu v jednom ze tří režimů může DMA výrazně snížit zátěž procesoru. Ve kterém z režimů DMA jste pracovali? Který z režimů považujete za efektivnější?