NA digitálně-analogový převodník ( Dacian , D / A , D2A nebo D-to-A ) je obvod určený k převodu digitálního vstupního signálu na analogový výstupní signál. Analogově-digitální převodník (ADC) pracuje opačně a transformuje analogový vstupní signál na digitální výstup.

V tomto článku komplexně diskutujeme o tom, jak obvody digitálně analogových a analogově digitálních převodníků fungují pomocí diagramů a vzorců.

V elektronice můžeme najít napětí a proudy, které se neustále mění s různými rozsahy a velikostmi.

V digitálních obvodech je napěťový signál ve dvou formách, buď jako logická vysoká nebo logická nízká logická úroveň, které představují binární hodnoty 1 nebo 0.

V analogově-digitálních převaděčích (ADC) je vstupní analogový signál reprezentován jako digitální velikost, zatímco digitálně-analogový převodník (DAC) převádí digitální velikost zpět na analogový signál.

Jak převaděče digitálních analogových signálů fungují

Proces digitálně-analogového převodu lze provést mnoha různými technikami.

Jedna známá metoda využívá síť odporů, známou jako žebříková síť.

Žebříková síť je navržena tak, aby přijímala vstupy zahrnující binární hodnoty typicky při 0 V nebo Vref a dodává výstupní napětí ekvivalentní velikosti binárního vstupu.

Obrázek níže ukazuje žebříkovou síť využívající 4 vstupní napětí, která představují 4 bity digitálních dat a stejnosměrný napěťový výstup.

Výstupní napětí je úměrné hodnotě digitálního vstupu vyjádřené rovnicí:

Řešení výše uvedeného příkladu získáme následující výstupní napětí:

Jak vidíme, digitální vstup 0110dvapřevede na analogový výstup 6 V.

Účelem žebříkové sítě je změnit 16 potenciálních binárních velikostí

přes 0000 až 1111 do jedné ze 16 veličin napětí v intervalech Vref/ 16.

Proto je možné zpracovat více binárních vstupů zahrnutím většího počtu žebříkových jednotek a dosáhnout vyšší kvantizace pro každý krok.

To znamená, předpokládejme, že pokud použijeme 10krokovou žebříkovou síť, dovolíme použít ke zvýšení množství krokového napětí nebo rozlišení na Vref/dva10nebo Vref/ 1024. V tomto případě, pokud bychom použili referenční napětí Vref= 10 V by generovalo výstupní napětí v krocích 10 V / 1024, nebo přibližně 10 mV.

Přidání většího počtu stupňů žebříku nám tedy dá proporcionálně vyšší rozlišení.

Typicky pro n počet kroků žebříku, to lze vyjádřit pomocí následujícího vzorce:

PROTIref/ dvan

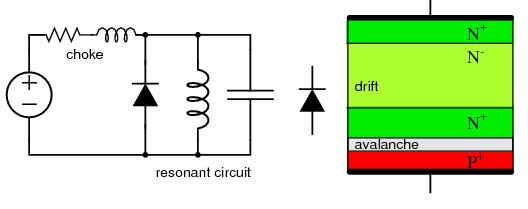

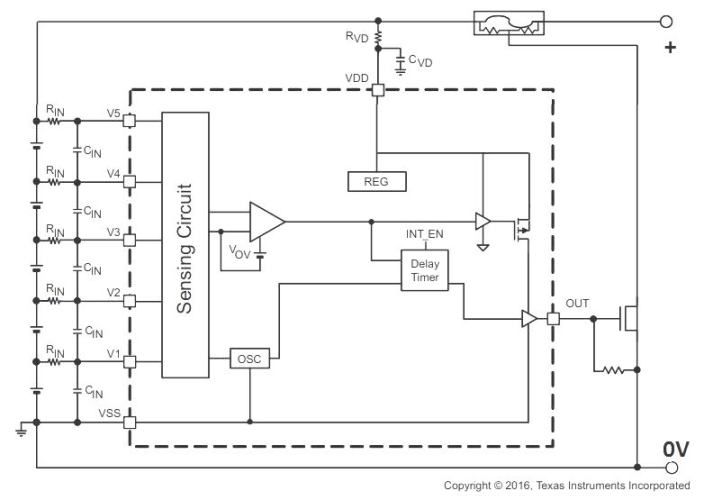

Blokové schéma DAC

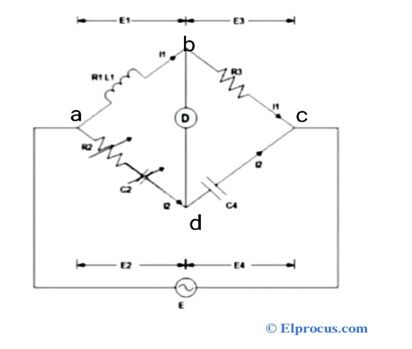

Na následujícím obrázku je blokové schéma standardního převodníku využívajícího žebříkovou síť označovanou jako žebřík R-2R. To lze vidět uzamčeno mezi zdrojem referenčního proudu a proudovými spínači.

Proudové spínače jsou spojeny s binárními spínači a vytvářejí výstupní proud úměrný vstupní binární hodnotě.

Binární vstupy přepínají příslušné nohy žebříku a umožňují výstupní proud, který je váženým součtem aktuální reference.

V případě potřeby lze k výstupům připojit rezistory pro interpretaci výsledku jako analogového výstupu.

Jak analogově-digitální převaděče fungují

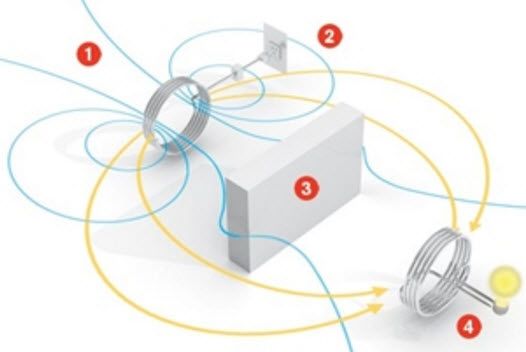

Dosud jsme diskutovali o tom, jak převést digitální na analogové signály, nyní se naučíme, jak postupovat opačně, tj. Převést analogový signál na digitální signál. To lze provést pomocí dobře známé metody zvané metoda dvojitého sklonu .

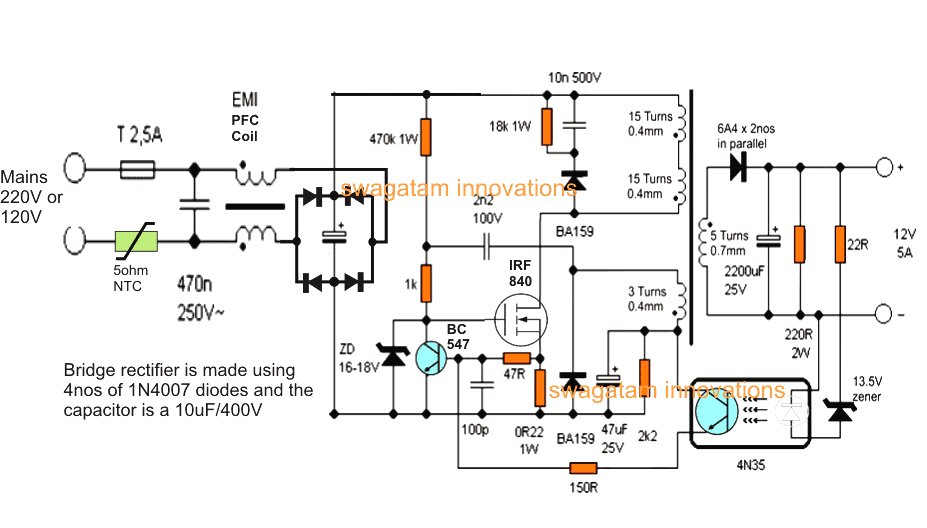

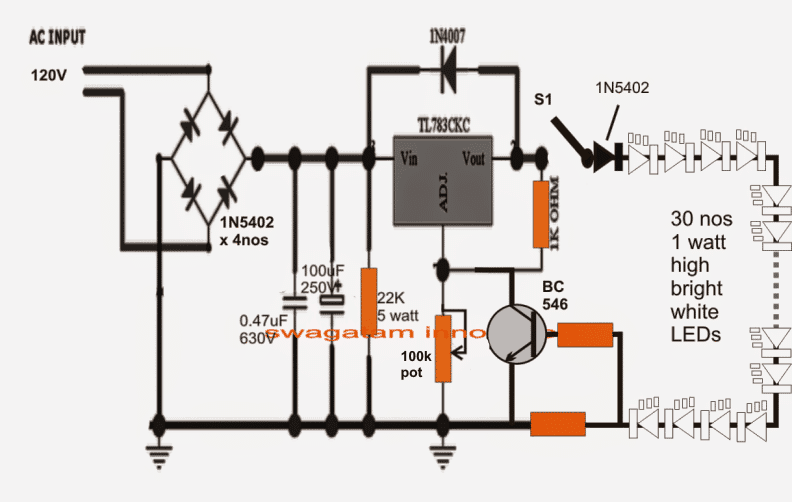

Následující obrázek ukazuje blokové schéma standardního převaděče ADC s dvojitým sklonem.

Zde se používá elektronický spínač k přenosu požadovaného analogového vstupního signálu na integrátor, nazývaný také generátor rampy. Tento generátor rampy může být ve formě kondenzátoru nabitého konstantním proudem pro generování lineární rampy. Tím se vytvoří požadovaná digitální konverze přes čítač, který pracuje pro kladné i záporné intervaly sklonu integrátoru.

Metodě lze porozumět s následujícím popisem:

O pevném časovém intervalu rozhoduje celý měřící rozsah počitadla. V tomto intervalu způsobí vstupní analogové napětí přivedené na integrátor vstupní napětí komparátoru na určitou kladnou úroveň.

S odkazem na část (b) výše uvedeného diagramu ukazuje, že napětí z integrátoru na konci pevného časového intervalu je vyšší než vstupní napětí, které je větší.

Po dokončení pevného časového intervalu je počet nastaven na 0, což vyzve elektronický spínač k připojení integrátoru k pevné úrovni vstupního vstupního napětí. Poté začne konstantní rychlostí klesat výstup integrátoru, který je také vstupem kondenzátoru.

Během této doby čítač stále postupuje, zatímco výstup integrátoru stále klesá konstantní rychlostí, dokud neklesne pod referenční napětí komparátoru. To způsobí, že výstup komparátoru změní stav a spustí fázi logické kontroly, aby zastavil počítání.

Uložená digitální velikost uvnitř čítače se stane digitálním výstupem převaděče.

Použití společných hodin a stupně integrátoru během kladných i záporných intervalů sklonu přidává určitou kompenzaci za řízení posunu frekvence hodin a meze přesnosti integrátoru.

Je možné škálovat výstup čítače podle preferencí uživatele vhodným nastavením referenční vstupní hodnoty a frekvence hodin. Můžeme mít počítadlo jako binární, BCD nebo v jiném digitálním formátu, pokud je požadováno.

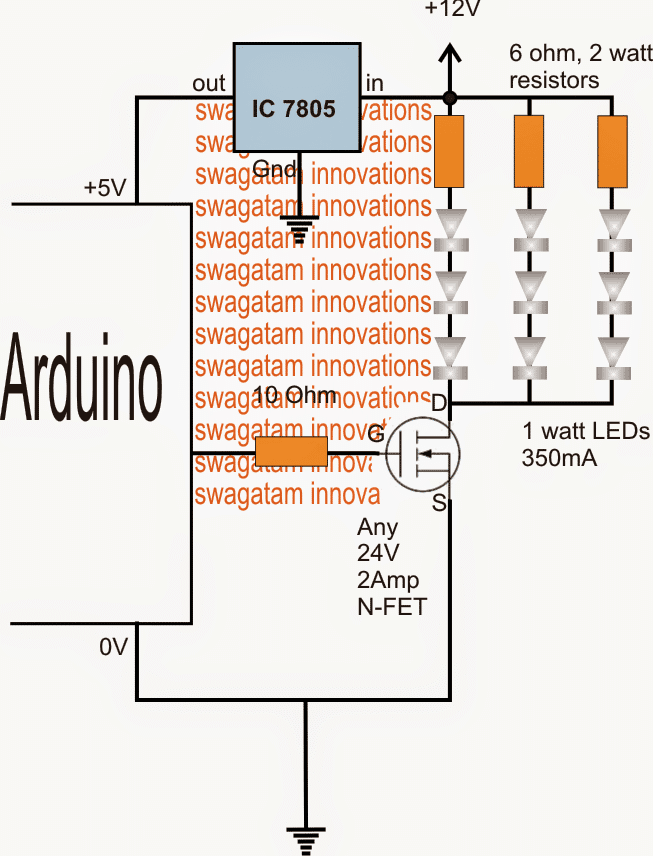

Používání žebříkové sítě

Metoda žebříkové sítě využívající stupně čítače a komparátoru je dalším ideálním způsobem, jak implementovat analogově-digitální převod. V této metodě počítadlo začíná počítat od nuly, což pohání žebříkovou síť, generuje stupňovité přírůstkové napětí připomínající schodiště (viz obrázek níže).

Tento proces umožňuje zvyšovat napětí s každým krokem počítání.

Komparátor sleduje toto přírůstkové napětí schodiště a porovnává jej s analogovým vstupním napětím. Jakmile komparátor zaznamená napětí schodiště nad analogovým vstupem, jeho výstup vyzve k zastavení počítání.

Hodnota čítače v tomto bodě se stává digitálním ekvivalentem analogového signálu.

Úroveň změny napětí generovaného kroky schodišťového signálu je určena množstvím použitých bitů.

Například 12stupňový čítač používající 10 V referenci bude provozovat 10stupňovou žebříkovou síť s krokovým napětím:

PROTIref/dva12= 10 V / 4096 = 2,4 mV

Tím se vytvoří konverzní rozlišení 2,4 mV. Čas potřebný k provedení převodu je určen hodinovou rychlostí čítače.

Pokud se pro provoz 12stupňového čítače použije takt 1 MHz, maximální doba potřebná pro převod bude:

4096 x 1 μs = 4096 μs ≈ 4,1 ms

Nejmenší možný počet konverzí za sekundu lze najít jako:

Ne. konverzí = 1 / 4,1 ms ≈ 244 konverzí za sekundu

Faktory, které ovlivňují proces převodu

Vzhledem k tomu, že některé převody mohou vyžadovat vyšší a některé mohou vyžadovat kratší dobu počítání, může být dobrá hodnota obvykle doba převodu = 4,1 ms / 2 = 2,05 ms.

Tím se vytvoří průměrný počet konverzí 2 x 244 = 488.

Pomalejší frekvence hodin by znamenala méně konverzí za sekundu.

Převaděč pracující s nižším počtem stupňů (nízké rozlišení) by měl vyšší rychlost převodu.

Přesnost převaděče je dána přesností měniče.

Předchozí: Jak vypočítat transformátory s feritovým jádrem Další: Ultrazvukový obvod indikátoru hladiny paliva